# ELECTRONICS 1 PART

#### PART 2 of FUNDAMENTALS OF ELECTRONIC DEVICES & BASIC ELECTRONIC CIRCUITS

# OPERATIONAL AMPLIFIERS

#### **DEFINITIONS**

Figure 1

Differential Pair

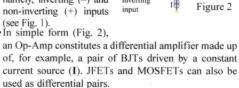

- A basic differential amplifier (see Electronics Chart Part One) enables mathematical difference Vint operation and can be modified to perform addition, integration and differentiation. Hence, the via differential amplifier is also designated as an Operational Amplifier (Op-Amp).

- An Op-Amp represents, in essence, a high-gain electronic circuit intended to amplify the difference in the signal voltages applied to its two input terminals, namely, inverting (-) and non-inverting (+) inputs

inverting

# **IDEAL OP-AMP CHARACTERISTICS**

- Nominal voltage gain, A → ∞

- Input impedance (at both inputs),  $\mathbf{Z_{in}} \rightarrow \infty$

- Output impedance,  $Z_0 \rightarrow 0$

- · Both transistors are identical.

- $\mathbf{v_0} = -\mathbf{A}\mathbf{v_{in1}} = \mathbf{A}\mathbf{v_{in2}}$ ; or, if  $\mathbf{v_{in1}} = \mathbf{v_{in2}}$ ,  $\mathbf{v_0} = \mathbf{0}$

- Bandwidth (BW) → ∞

- · With bipolar transistors, it may be difficult to achieve a very high-input impedance.

- JFET and MOSFET provide high-input impedance capabilities.

# OP-AMP OPERATIONAL PARAMETERS

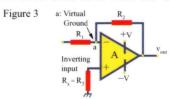

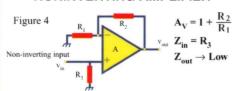

In reference to typical inverting (Fig. 3, above right) and non-inverting (Fig. 4) modes of operational characteristics:

- INPUT BIAS CURRENT: This is the emitter current in the differential amplifier for active region operation of the pair of BJTs (e.g. 0.05µA for 741 OP-AMP) which comes through  $R_2$  so that  $v_{out} = (0.05 \times 10^{-6} \times R_2)$  volts. This could be large enough to saturate the output. Saturation is overcome by introducing  $\mathbf{R}_{\mathbf{x}} = \mathbf{R}_{\mathbf{1}} \parallel \mathbf{R}_{\mathbf{2}}$  and made adjustable to compensate for input offset current due to any dissimilarities in the differential pair configuration (Fig. 3).

- INPUT OFFSET VOLTAGE (≈ ± 60mV): It is required at the input as a counter voltage to offset the finite unbalance voltage due to unequal current flowing through the differential pair devices in the OP-AMP, so that this balancing gives zero output voltage.

- CMRR: When the OP-AMP is ideally balanced at the input, the output voltage = 0, i.e.  $v_{in1} = v_{in2}$ , and this circuit can reject common-mode signals due to its common-mode gain  $(A_a) = 0$ . For differential mode signals  $(v_{in1} - v_{in2})$ , the gain  $(A_d) \rightarrow \infty$ . The ratio  $A_d/A_c$ common-mode rejection ratio (CMRR). In practical OP-AMPs,  $A_c > 0$  and  $A_d < \infty$ ; or, CMRR is finite and indicates the extent of balance in the OP-AMP

- (A figure of merit parameter).

OUTPUT VOLTAGE SWING: This is the peak output swing with reference to zero at the output. It is limited by power supply voltages used ( $\approx 80$  percent of power supply voltage  $\pm V$ ).

- INPUT VOLTAGE SWING: Input common-mode voltage swing is limited by the saturation of the differential amplifier at the input: ( $\approx 30$  percent of power supply voltage  $\pm V$ ).

- SLEW RATE: Maximum rate at which the output voltage can change (volts/microsecond). In ideal OP-AMPs, slew-rate  $\rightarrow \infty$ .

- OTHER PARAMETERS: (1) Bandwidth; (2) Maximum output current available when the output terminal is set to ground; (3) PSRR: Power supply rejection ratio: Change in input offset voltage to corresponding change in one of the power supply voltages  $(\pm V)$ . Ideally, PSRR = 0; in practice, it is of the order of a few uV/V.

#### FREQUENCY ROLL-OFF

It is the fall-off of the voltage gain at high frequencies. This is indicated by gain-bandwidth product. Roll-off to higher frequencies is achieved by frequency compensation.

#### INVERTING AMPLIFIER (VIRTUAL GROUND AMPLIFIER)

- Output impedance with feedback

- $\simeq$  Output impedance of the OP-AMP × Closed-loop gain (Open - loop gain)

- Node a is almost at ground potential.

- Closed-loop voltage gain  $v_{out} / v_{in} = -R_2/R_1$

- Input impedance = R<sub>1</sub>

- Output impedance =  $R_0$

#### **NONINVERTING AMPLIFIER**

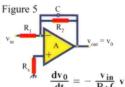

#### **INTEGRATOR (LOW-PASS FILTER)**

·R<sub>2</sub>: Provides negative feedback for lowoutput impedance needs, but it also distorts the output.

$\frac{dv_0}{dt} = -\frac{v_{in}}{R_1C} v_0 = -\left(\frac{1}{R_1C}\right) \times \int v_{in} dt$

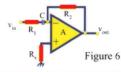

# **DIFFERENTIATOR (HIGH-PASS FILTER)**

· Inverse operation of the integrator circuit.

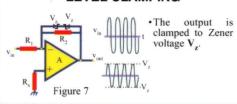

#### **LEVEL CLAMPING**

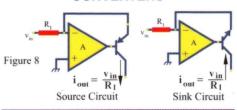

#### LINEAR VOLTAGE-TO-CURRENT CONVERTERS

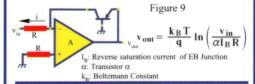

#### LOGARITHMIC AMPLIFIER

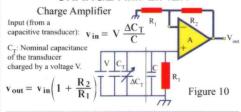

#### CHARGE AMPLIFIER

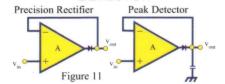

#### **PRECISION RECTIFIER & PEAK DETECTOR**

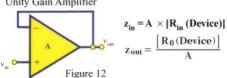

## **VOLTAGE FOLLOWER** (UNITY GAIN AMPLIFIER)

Unity Gain Amplifier

The output voltage "follows" the input voltage. Used as a buffer amplifier with high-input/low-output impedance realization.

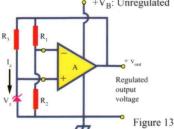

#### REGULATED POWER SUPPLY

The Zener diode offers a constant reference voltage  $(V_2)$ . Bias derived from the unregulated voltage  $(V_B)$ , via potential division by  $R_1$  and  $R_2$  and the Zener reference voltage, are compared by an inverting amplifier to provide a stable output voltage.  $v_{out} = V_z (1 + R_1 / R_2)$  and  $I_z = (v_{out} - V_z) / R_3$

+V<sub>R</sub>: Unregulated

# **UNIPOLAR DEVICES FIELD EFFECT TRANSISTORS (FETs)**

#### **DEFINITIONS**

- The device current is decided by one type of current carrier only (unipolar).

- The device interior current is controlled by an electric field applied in the path of the current carriers.

#### **FET TYPES**

- JFET (Junction Field Effect Transistor): In the JFET, the resistance of the current path is modulated by the application of bias voltages to PN junctions adjacent to it.

- MOSFET (Metal-Oxide Semiconductor FET): In MOSFET, there are no junctions. The controlling electric field is applied via an insulating layer to regulate the resistance of a main conducting path.

#### **FET OPERATION MODES**

- Depletion mode operation: The controlling electric field reduces the number of carriers available for conduction.

- Enhancement mode operation: Application of electric field causes an increase in the majority-carrier density in the conducting regions of the transistor.

#### JFET: DEVICE OPERATION

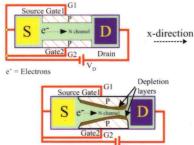

JFET: Device Operation

Figure 14a

Due to the application of the voltage across source (S)to-drain (D), electrons flow from S to D (majority carrier flow). The path between S-to-D has an ohmic resistance. Therefore, flow of electron current would cause a voltage drop and the potential at any point along this path (x-direction) increases from the source to drain (becoming more positive towards the drain end). Since the gates (tied together) are connected to the source, the N-region of the channel and the regions of the gate would form a reverse-biased PN junction. The extent of reverse bias increases progressively from the

source side to drain side. Correspondingly, the depletion layers formed will be wider near the drain side as shown. Normally, the P-type gates (G1 and G2) are heavily doped relative to the N-channel region. Therefore, channel has (relatively) high resistance. Hence, the depletion layer widens predominantly into the channel region. Suppose VD is increased. Consequently, the depletion layer into the channel widens more. As a result, eventually the two (top and bottom) depletion layers meet each other. Therefore, the channel is closed, not permitting the flow of electrons through it. This condition is known as pinch-off.

#### OUTPUT CHARACTERISTICS OF JFET

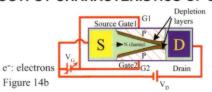

Suppose an additional bias  $V_{\mathbf{G}}$  is applied between the gates and the source terminals (Figure 14b):

Suppose,  $V_G = 0$ . In the absence of drain current, the depletion layer is uniform along the channel. As VD increases, ID increases. Corresponding voltage drop along the channel causes a wedge-shaped path due to reasons discussed before. Upon pinch-off, the drain current remains constant at a saturated value.

• When  $V_G$  is applied: This provides additional reversebias. Therefore, pinch-off will occur at lower  $\boldsymbol{V}_{\boldsymbol{D}}$  and the corresponding  $V_{D(sat)}$  will also be smaller. Hence, application of  $V_G$  modulates the channel dimension and reduces In. This is a depletion mode operation. Channel current decreases as the gate voltage is increased.

#### LINEAR OPERATION OF JFET

Linear Operation of JFET

Suppose channel is lightly doped relative to the gates, i.e. N<sub>a(gate)</sub> >> N<sub>d(channel)</sub>. .. Thickness of depletion

layer in the N-channel is  $\mathbf{d_n} \cong \left[ 2\varepsilon \frac{(V_0 + V_G)}{eN_D} \right]^{\frac{1}{2}}$ .  $\therefore$

$[V_0$ : Contact potential,  $N_a$  and  $N_d$  are acceptor and donor concentrations; E: Permittivity of the channel]. Let  $V_{p0}$  be the value of  $V_{G}$  at which pinch-off occurs. The corresponding change in  $I_D = 0$ . For  $V_G < V_{P0}$ ,

$$\mathbf{I}_{\mathrm{D}} \approx \mathbf{G}_{\mathrm{0}} \left[ \mathbf{I} - \left( \frac{\mathbf{V}_{\mathrm{G}}}{\mathbf{V}_{\mathrm{P}_{\mathrm{0}}}} \right)^{\frac{1}{2}} \right] \mathbf{V}_{\mathrm{D}},$$

where  $G_0$  = channel conductance with zero bias ( $V_G$  = 0) condition:  $G_0 = (eN_d\mu_e) \times$

[Area of cross-section of the channel / Length of the channell

e: electronic charge; μ<sub>e</sub>: electron mobility.

#### JFET OPERATION

Upon pinch-off:

$$I_{DS} = I_{D_0} \left[ 1 - \frac{3V_G}{V_P} + 2 \left( \frac{V_G}{V_P} \right)^{\frac{3}{2}} \right]$$

$$\mathbf{g_m} = \left. \frac{\partial \mathbf{I_{DS}}}{\partial \mathbf{V_G}} \right|_{\mathbf{V_D}} = -\left. \mathbf{I_{D_0}} \frac{3 \mathbf{V_D}}{\mathbf{V_p^2}} \right| 1 - \left( \frac{\mathbf{V_G}}{\mathbf{V_P}} \right)^{\frac{1}{2}}$$

g<sub>m</sub> ≜ Mutual/transfer conductance

= Max

$$g_m = g_m|_{V_G = 0} = g_{m_0} = \frac{-3I_{D_0}}{V_P} = -G_0$$

= Conductance of the channel with zero bias

$$\mathbf{g}_{\mathbf{m}} \cong \mathbf{g}_{\mathbf{m}_0} \left[ 1 - \left( \frac{\mathbf{V}_{\mathbf{G}}}{\mathbf{V}_{\mathbf{P}}} \right)^{\frac{1}{2}} \right]$$

#### MOSFET

#### **DEFINITIONS**

⇒ Induced channel device/Insulated Gate FET (IG

- The gate is totally insulated from the semiconductor by a thin layer of SiO2.

- The voltage applied at the gate induces a conducting channel within the semiconductor and modulates its conductivity.

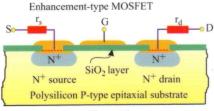

#### **ENHANCEMENT TYPE MOSFET**

Figure 16

SiO<sub>2</sub>⇒100 to 300 A° (Thermally grown insulation layer)

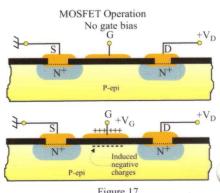

Figure 17

#### MOSFET OPERATION

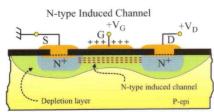

Suppose no gate voltage is applied. Then N+P junction at the source, as well as PN+ junction at the drain, are reverse-biased. Therefore, no drain current flows. Suppose a small  $+V_G$  is applied at the gate. The positive voltage at the top of the  $SiO_2$  dielectric would induce negative charges below this layer. These negative charges will deplete the holes of the P-epilayer, exposing negatively charged acceptor ions, i.e. a depletion layer will be formed just below the gate as shown in Fig. 17. A further increase in  $+V_G$  will induce more and more negative charges below the gate, with the result being a copious accumulation of negative charges below the gate forming an induced-layer of negative charges constituting a "channel" (induced channel) between the source and the drain as shown in Fig.18.

Figure 18

Once the channel is induced between the S and D, the electrons flow through this channel, with the result being a drain current. Therefore, the induced channel constitutes an ohmic path. The conductivity of this channel is dependent on the magnitude of VG. In other words, the channel conductivity is modulated by V<sub>G</sub>. Therefore, the more the  $V_G$ , the more will be  $I_D$ . Thus, the device operates in enhancement mode.

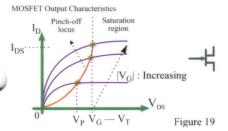

#### MOSFET OUTPUT CHARACTERISTICS

Analysis: Let voltage at x along the channel be V(x).

$$\boldsymbol{I}_{D} = \left(\frac{\mu_{e} C_{g}}{L^{2}}\right) \! \left(\boldsymbol{V}_{G} - \boldsymbol{V}_{T} - \boldsymbol{V}_{D}/2\right) \boldsymbol{V}_{D} \Rightarrow \text{This } \boldsymbol{I}_{\boldsymbol{D}} \text{ versus}$$

$V_D$  is valid as long as  $V_G - V(x) > V_T$ . Note: L: Channel length. At some gate voltage  $V_{G_1}$  with  $V(x) = V_D$ , the channel is turned open and the flow of charges along the channel becomes constant, i.e. at  $V_D = V_{G_1} - V_T$ ,

$$I_{ds} = \frac{\left(\frac{\mu_e C_g}{L^2}\right) \left(V_{G1} - V_T\right)^2}{2}$$

$$\frac{\partial I_D}{\partial V_G} \bigg|_{V} \Rightarrow g_m = \mu_e C_g \frac{V_D}{L^2}$$

$$I_{DS} = I_{D} \big|_{V_{D} = |V_{G} - |V_{T}|} = \frac{\mu_{e} C_{g}}{2L^{2}} \big(V_{G} - V_{T}\big)^{2} = g_{m} \frac{V_{D}}{2}$$

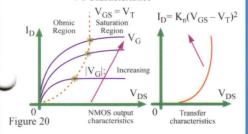

#### V-I CHARACTERISTICS OF **ENHANCEMENT-TYPE MOSFET**

V-I Characteristics

• Ohmic Region (Triode Region) Here  $V_{DS} \le V_{GS} - V_T$  and the V-I characteristic is

$$I_D = K_n [2(V_{GS} - V_T)V_{DS} - V_{DS}^2], \text{ where}$$

$$\mathbf{K_n} = \frac{\mu_e \, \epsilon_o \, \epsilon_{ox}}{2t_{ox}} \frac{W}{L} = \frac{\mu_e \, C_{ox}}{2} \left(\frac{W}{L}\right) \text{ and } \mu_e = \text{surface}$$

mobility of electrons:  $\mu_e = 800 \text{cm}^2 / \text{volt-sec}$  (in Si).

$\varepsilon_0$  = permittivity of free space ( = 8.85 x 10<sup>-14</sup> F/cm)

$\varepsilon_{ox}$  = dielectric constant of SiO<sub>2</sub> ( $\cong$  4);

$\mathbf{t}_{ox}$  = thickness of the oxide;  $\mathbf{C}_{ox} = \varepsilon_o \varepsilon_{ox} \mathbf{LW}/\mathbf{t}_{ox}$  $\mathbf{C}_{ox}$ : Capacitance of SiO<sub>2</sub> layer

Dividing locus between saturation and ohmic regions is given by substituting  $V_{DS} = (V_{GS} - V_T)$ :

$$I_D = K_n V_{DS}^2 = \frac{\mu_e C_{ox} W}{2L} V_{DS}^2$$

This locus is shown by the dotted line in Figure 20.

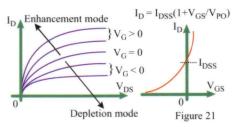

- SATURATION REGION: Here,  $V_{DS} \ge V_{GS} V_{T}$ , and the current  $I_{D}$  is approximately constant as shown in Fig. 20. The transfer characteristic is obtained by replacing  $V_{DS}$  by  $V_{GS} - V_T$ :  $I_D = K_n (V_{GS} - V_T)^2$ . A plot of the transfer characteristic is shown in Fig. 20.

- **CUTOFF REGION**: Here,  $V_{GS} < V_{T}$ , and thus  $I_{D} = 0$ . The device is *OFF* in this region and is used in switching applications in this mode.

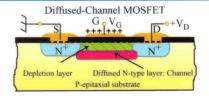

#### **DIFFUSED-CHANNEL** (DEPLETION-TYPE) MOSFET

- · Diffused-channed MOSFET can be operated both as depletion mode or as enhancement mode device.

- The device has a thin N-type layer of the same conductivity as source or drain and is diffused below the gate.

- When the gate has a small negative bias, the resulting positive charges in this diffused region cause the depletion layer (channel conductance) to be reduced. Thus, negative bias on gate enables depletion mode operation.

# QuickStudy.

When a positive bias is applied, more electrons are drawn into the channel causing more carrier population, i.e. channel conductance is increased. Hence, more current would flow; or, an increase in +VG would increase In ⇒ enhancement mode operation. V-I characteristics indicate that circuit operations of diffused channel MOSFET are similar to those of JFET.

# SMALL-SIGNAL **EQUIVALENT CIRCUIT &** FREQUENCY RESPONSE OF FETs

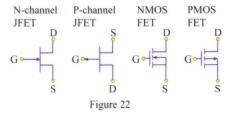

Normal symbolic representations of the JFETs and the MOSFETs are shown in Fig. 22.

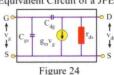

Approximate Low Frequency **Equivalent Circuits**

High Frequency Equivalent Circuit of a JFET

Current in an FET is carried by majority carriers drifting under the influence of an electric field, whereas in the bipolar transistor, current is transported by means of diffusing minority carriers. Since drift velocities in semiconductors are usually very much higher than diffusion velocities, carrier transit times are much shorter in FETs than in bipolar transistors. For this reason, one might expect FETs to have a much more extended high-frequency range than bipolar devices. A limitation to the high-frequency performance or the switching speed of a FET is the gate-channel capacitance, which must be charged via the channel resistance. The resulting time constant determines the upper limit

equals  $g_m/2\pi C_g$  , is normally taken as a figure of merit to indicate the high-frequency response of a particular device.  $\frac{g_m}{C} = \mu_e \frac{V_g - V_T}{L^2}$ ;  $C_g$ : Total gate capacitance

of the frequency response. The gain × bandwidth prod-

uct, which can be derived from the equivalent circuit and

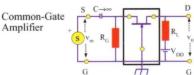

#### **COMMON-GATE AMPLIFIER**

Common-gate (CG) FET amplifier circuit and its equivalent circuits Fig. 25

$$\begin{split} \mathbf{A}_{v} = & \frac{\mathbf{v}_{0}}{\mathbf{v}_{in}} = \frac{(\mu + 1) \, \mathbf{R}_{L}}{\mathbf{r}_{d} + \mathbf{R}_{L}} \cong \mathbf{g}_{m} \, \mathbf{R}_{L} \, \text{for} \\ & \mu = \mathbf{g}_{m} \mathbf{r}_{d} >> 1, \, \mathbf{r}_{d} >> \, \mathbf{R}_{L} \\ \mathbf{R}_{i} = & \frac{\mathbf{v}_{in}}{i_{1}} = \frac{\mathbf{R}_{L} + \mathbf{r}_{d}}{\mu + 1} \cong \frac{1}{g_{m}} \, \text{for} \, \mathbf{r}_{d} >> \, \mathbf{R}_{L}; \\ \mathbf{R}_{0} = & \frac{\mathbf{v}_{0}}{i_{2}} = \mathbf{r}_{d} + (\mu + 1) \mathbf{R}_{G} \cong \mathbf{r}_{d} + \mu \mathbf{R}_{G} \end{split}$$

(µ: Amplification factor)

Note: For CG configuration, the output resistance is very large and can be considered as infinite; the input resistance is relatively low. Voltage gain is dependent on R1, and its maximum value is about  $\mu$  . CG configuration in FET is the counterpart of CB configuration in BJTs.

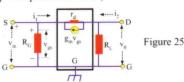

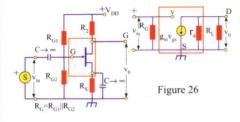

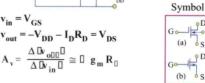

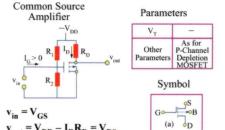

#### COMMON-SOURCE AMPLIFIER

A common-source (CS) FET amplifier (with the dc biasing circuitry) and its small signal equivalent circuit are shown in Fig. 26.

Common-Source Amplifier

$$\begin{split} R_{in} \rightarrow & \infty; \ R_0 = r_d; \ v_0 = -g_m \ (r_d \parallel R_L) \ v_{in} \\ A_v = & \frac{v_0}{v_{in}} = -gm \ (r_d \parallel R_L) \cong -g_m R_L \ \text{for} \ r_d >> R_L \\ & \left(\frac{v_0}{v_{in}}\right)_{max} = -g_m r_d = \mu >> 1 \end{split}$$

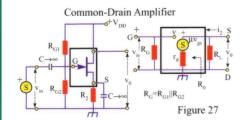

#### COMMON-DRAIN AMPLIFIER

A common-drain (CD) FET amplifier (with the biasing circuitry) and its small-signal equivalent circuit are shown in Fig. 27.

$$\begin{split} R_{0} &= \frac{v_{o}}{i_{2}} = \frac{r_{d}}{1 + \mu} \cong \frac{r_{d}}{\mu} = \frac{1}{g_{m}} \text{ for } \mu >> 1 \\ A_{v} &= \frac{v_{0}}{v_{in}} = \frac{\mu R_{L}}{(1 + \mu) R_{L} + r_{d}} \cong \frac{g_{m} R_{L}}{1 + g_{m} R_{L}} \end{split}$$

For  $g_m R_L >> 1$ , the voltage gain is close to unity. The CD configuration is therefore called the source follower (SF), since the source voltage follows the input gate signal. The CS configuration in FET is the counterpart of the CC configuration in BJT.

# **Summary on JFETs & MOSFETs**

#### N-CHANNEL JFET

Figure 28

| Vout | $=-V_{D}$ | $-I_{D}R_{D}$ | $=V_{DS}$ | $-I_SR_S$ | Symbol |

|------|-----------|---------------|-----------|-----------|--------|

|      |           |               |           |           |        |

$$A_{v} = \frac{\Delta D v_{000}}{\Delta D v_{in}} = \frac{D}{R_{0}} \frac{R_{0}}{R_{0} + \frac{1}{g_{m}}}$$

- On-State: v<sub>GS</sub> > V<sub>T</sub>

- Satration Region:  $v_{DS} \ge v_{GS} V_{T}$  $i_D = K(v_{GS} - V_T)^2 (1 + \lambda V_{DS})$

- Triode Region:  $V_{DS} \le V_{GS} V_{T}$

$$i_D = K[2(v_{GS} - V_T)v_{DS} - v_{DS}^2]$$

• VA: A FET Parameter

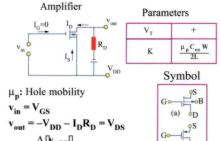

#### P-CHANNEL JFET

Figure 29

$$V_{out} = -V_{DD} - I_D R_D = V_{DS} - I_S R_S$$

$$A_{v} = \frac{\Delta D v_{odd} D}{\Delta D v_{in} D} = \frac{D R_{0}}{R_{0} + \frac{1}{g_{m}}}$$

- On-State:  $v_{GS} \le V_T$

- Satration Region:  $v_{DS} \leq v_{GS} V_{T}$

$$i_D = K(V_{GS} - V_T)^2 (1 + \lambda V_{DS})$$

• Triode Region:  $V_{DS} \ge V_{GS} - V_{T}$

$$i_D = K[2(v_{GS} - V_T)v_{DS} - v_{DS}^2]$$

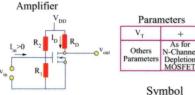

#### N-CHANNEL DEPLETION MOSFET

Figure 30

| Parameters |                             |  |  |  |  |

|------------|-----------------------------|--|--|--|--|

| $V_T$      | _                           |  |  |  |  |

| K          | $\frac{\mu_n C_{ox} W}{2L}$ |  |  |  |  |

| Others     | As for<br>N-Channel<br>JFET |  |  |  |  |

Common-Source

- (a) Conventional

- (b) When substrate/body "B" connected to source

Note: Different states and regions of operation: ⇒ Same as for N-channel JFET

U.S.\$4.95

Author: Dr. P.S. Neelakanta C. Eng., Fellow IEE

# N-CHANNEL ENHANCEMENT MOSFET

Figure 31

(a) Conventional

Common Source

Common Source

(b) When substrate/body "B" connected to source

Note: Different states and regions of operation: ⇒ Same as for N-channel JFET

#### P-CHANNEL DEPLETION MOSFET

Figure 32

- (a) Conventional

- (b) When substrate/body "B" connected to source

Note: Different states and regions of operation: ⇒ Same as for P-channel JFET

#### P-CHANNEL ENHANCEMENT MOSFET

Figure 33

- (a) Conventional

- (b) When substrate/body "B" connected to source

Note: Different states and regions of operation: ⇒ Same as for P-channel JFET

Customer Hotline # 1.800.230.9522 We welcome your feedback so we can maintain and exceed your expectations.

# free downloads

#### COMPARISON OF FET AMPLIFIERS

|                                | CG               | CS                              | CD(SF)*                       |

|--------------------------------|------------------|---------------------------------|-------------------------------|

| R <sub>in</sub>                | 1/g <sub>m</sub> | ∞                               | 000                           |

| $R_0$                          | ∞                | r <sub>d</sub>                  | 1/g <sub>m</sub>              |

| $A_{v} = \frac{v_{0}}{v_{in}}$ | $g_m R_L$        | - g <sub>m</sub> R <sub>L</sub> | $\frac{g_m R_L}{g_m R_L + 1}$ |

\*SF=Source Follower

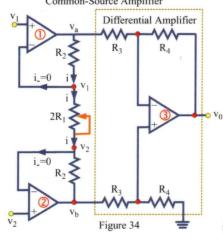

#### **OP-AMPS REVISITED**

INSTRUMENTATION AMPLIFIER - a highperformance differential amplifier with high-input

- $V_0 = -(R_4/R_3) (1 + R_2/R_1) (V_1 V_2)$ Input impedance presented at both inputs tends to

- Output impedance of the differential amplifier tends

- Application: To amplify differential signal(s) from transducers / sensors.

R<sub>1</sub> can be adjusted to achieve null-offset.

Common-Source Amplifier

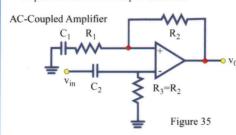

#### AC-COUPLED NON-INVERTING AMPLIFIER:

- Capacitively coupling an OP-AMP reduces the dc offset considerably.

- Provision of  $\mathbf{R}_3$  is mandated to facilitate continuous dc path for each of the input terminals.

#### A SUMMARY ON OP-AMPS

- OP-AMPS in practical circuits offer performance matching theoretical estimations.

An OP-AMP consists of:

- (a) An inverting input terminal;

- (b) A non-inverting input terminal;

- (c) An output terminal;

- (c) An output terminal;

(d) Two power supply terminals + and -, with a common circuit ground.

Ideally, an OP-AMP responds to the two inputs (+ v<sub>in1</sub>) and (- v<sub>in2</sub>) to yield an output V<sub>0</sub> = A(v<sub>in1</sub> v<sub>in2</sub>); A is known as open-loop gain, which is very large (Ideally A → ∞; in practice, A ~ 10<sup>4</sup> to 10<sup>6</sup>).

An ideal OP-AMP has an infinite input impedance (at both input terminals) and a zero output impedance.

- both input terminals) and a zero output impedance. With a negative feedback, the closed-loop gains are:

- For inverting input,  $v_0/v_{in1} = R_2/R_1$ For non-inverting input,  $v_0/v_{in2} = (1 + R_2/R_1)$

NOTICE TO STUDENT: Due to its condensed format, use this **QUICKSTUDY** \* guide as an outline of the basics of Electronics and not as a replacement for assigned course work. ©2001, 2003 Barcharts, Inc. 0407

ISBN-13: 978-157222530-5 ISBN-10: 157222530-0